5.7. 流水线:让 CPU 运行得更快

我们的四级 CPU 需要四个周期来执行一条指令:第一个周期用于从内存中获取指令;第二个周期用于解码指令并从寄存器文件中读取操作数;第三个周期用于 ALU 执行操作;第四个周期将 ALU 结果写回到寄存器文件中的寄存器。执行一系列 N 条指令需要 4N 个时钟周期,因为每个指令都是由 CPU 按顺序一次执行一条。

图 1. 执行三条指令总共需要 12 个周期。

图 1 显示三条指令总共需要 12 个周期来执行,每条指令需要 4 个周期,因此 CPI 为 4(CPI 是执行一条指令的平均周期数)。但是,可以改进 CPU 的控制电路以实现更好(更低)的 CPI 值。

考虑到执行模式,即每条指令需要四个周期才能执行,然后下一条指令需要四个周期,依此类推,与实现每个阶段相关的 CPU 电路每四个周期仅积极参与一次指令执行。例如,在提取阶段之后,CPU 中的提取电路不会用于执行与接下来三个时钟周期执行指令相关的任何有用操作。但是,如果提取电路可以在接下来的三个周期继续积极执行后续指令的提取部分,则 CPU 可以每四个周期完成一条以上指令的执行。

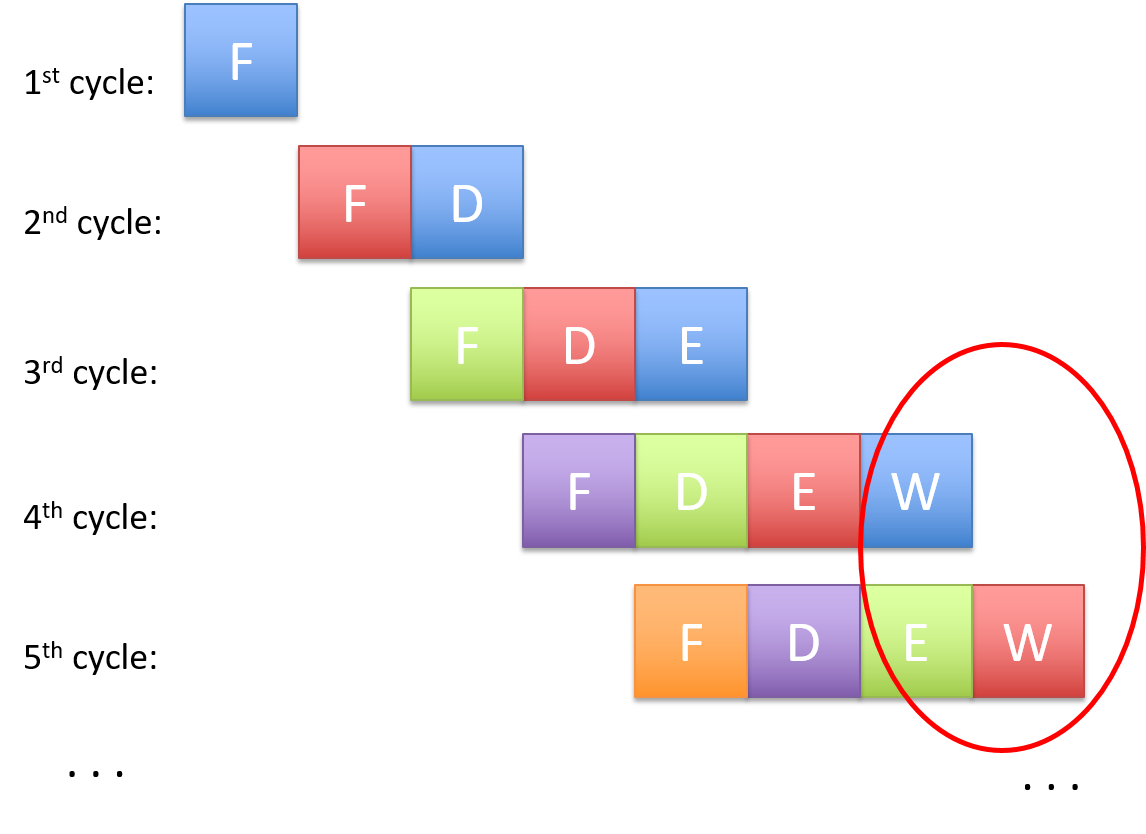

CPU 流水线 是在当前指令完全完成执行之前开始执行下一条指令的理念。CPU 流水线按顺序执行指令,但它允许一系列指令的执行重叠。例如,在第一个周期中,第一条指令进入其获取执行阶段。在第二个周期中,第一条指令移至其解码阶段,第二条指令同时进入其获取阶段。在第三个周期中,第一条指令移至其执行阶段,第二条指令移至其解码阶段,第三条指令从内存中获取。在第四个周期中,第一条指令移至其写回阶段并完成,第二条指令移至其执行阶段,第三条指令移至其解码阶段,第四条指令进入其获取阶段。此时,CPU 指令流水线已满 - 每个 CPU 阶段都在积极执行程序指令,其中每个后续指令都比其前一个指令落后一个阶段。当流水线已满时,CPU 每个时钟周期完成一条指令的执行!

图 2. 流水线:重叠指令执行,实现每周期完成一条指令。圆圈表示 CPU 已达到每周期完成一条指令的稳定状态。

图 2 展示了通过我们的 CPU 执行流水线指令的示例。从第四个时钟周期开始,流水线填满,这意味着 CPU 每个周期完成一条指令的执行,实现 CPI 为 1(如 图 2 中的圆圈所示)。请注意,执行单个指令所需的总周期数(指令 延迟)在流水线执行中并没有减少——每条指令仍然需要四个周期才能执行。相反,通过在流水线的不同阶段以交错的方式重叠执行顺序指令,流水线增加了指令 吞吐量,即 CPU 在给定时间段内可以执行的指令数量。

自 20 世纪 70 年代以来,计算机架构师一直使用流水线技术来大幅提高微处理器的性能。然而,与不支持流水线执行的 CPU 设计相比,流水线技术的代价是 CPU 设计更为复杂。支持流水线技术需要额外的存储和控制电路。例如,可能需要多个指令寄存器来存储当前流水线中的多条指令。这种增加的复杂性几乎总是值得的,因为流水线技术可以大幅提高 CPI。因此,大多数现代微处理器都实现了流水线执行。

流水线的概念也用于计算机科学的其他领域,以加快执行速度,并且该概念也适用于许多非计算机科学应用。例如,考虑使用一台洗衣机洗多批衣物的任务。如果完成一次洗衣包括四个步骤(洗涤、烘干、折叠和收起衣服),那么在洗完第一批衣物后,第二批衣物可以放入洗衣机,而第一批衣物则放在烘干机中,这样可以重叠洗涤每批衣物,从而加快洗涤四批衣物所需的总时间。工厂装配线是流水线的另一个例子。

在讨论 CPU 如何执行程序指令和 CPU 流水线时,我们使用了一个简单的四级流水线和一个示例 ADD 指令。要执行在内存和寄存器之间加载和存储值的指令,则使用五级流水线。五级流水线包括用于内存访问的内存阶段:提取-解码-执行-内存-写回。不同的处理器可能具有比典型的五级流水线更少或更多的流水线阶段。例如,最初的 ARM 架构有三个阶段(提取、解码和执行,其中执行阶段执行 ALU 执行和寄存器文件写回功能)。较新的 ARM 架构的流水线中有五个以上的阶段。最初的 Intel Pentium 架构有五级流水线,但后来的架构有更多流水线阶段。例如,Intel Core i7 有 14 级流水线。